集成电路设计 从概念到实体的技术蓝图

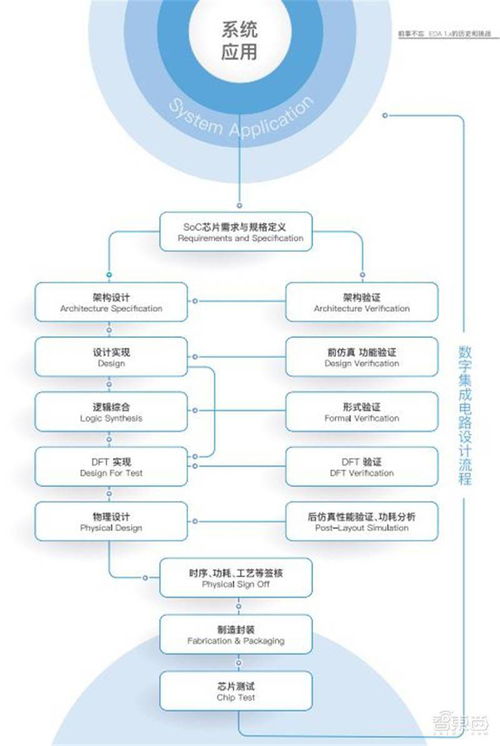

集成电路设计是现代电子工业的核心环节,它涉及将复杂的电子系统功能转化为可在微小硅片上实现的物理结构。设计过程通常包括多个层次,从系统级设计到物理实现,每一步都至关重要。

在系统级设计阶段,工程师定义芯片的整体功能和性能指标,例如处理速度、功耗和面积。这一阶段通常使用高级建模语言(如SystemVerilog或VHDL)进行行为描述,确保设计满足应用需求。

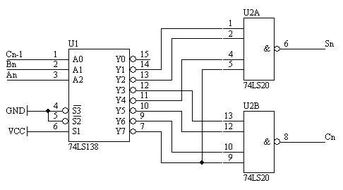

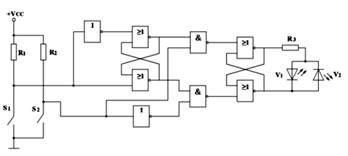

接下来是逻辑设计,工程师将系统功能转化为逻辑门和寄存器传输级(RTL)代码。这一步骤通过仿真验证逻辑正确性,并优化电路结构以减少延迟和功耗。常用的工具有Synopsys Design Compiler和Cadence Genus,它们帮助自动化逻辑综合过程。

物理设计是集成电路设计的关键视图之一,涉及将逻辑电路映射到实际的硅片布局。这包括布局规划、电源网络设计、时钟树综合和布线。工具如Cadence Innovus和Synopsys IC Compiler支持这一过程,确保电路在制造后能稳定运行。物理设计还必须考虑制造约束,例如光刻限制和热管理,以避免缺陷。

验证贯穿整个设计流程,包括功能验证、时序验证和物理验证。通过仿真、形式验证和原型测试,工程师确保芯片在真实环境中无误工作。随着工艺节点不断缩小(如7纳米或5纳米),设计复杂度增加,验证变得尤为重要。

集成电路设计视图不仅关注技术实现,还涉及多学科协作。设计师需要与工艺工程师、软件开发者紧密合作,以平衡性能、成本和上市时间。随着人工智能和物联网的兴起,集成电路设计将更注重能效和集成度,推动创新应用发展。集成电路设计是电子技术进步的基础,它通过精密的视图规划,将创意转化为改变世界的芯片产品。

如若转载,请注明出处:http://www.jabouyo.com/product/24.html

更新时间:2026-04-30 17:20:21